The QMA7981 is a single chip three-axis accelerometer. This surface-mount, small sized chip has integrated acceleration transducer with signal conditioning ASIC, sensing tilt, motion, shock and vibration, targeted for applications such as screen rotation, step counting, sleep quality, gaming and personal navigation in mobile and wearable smart devices.

The QMA7981 is based on our state-of-the-art, high resolution single crystal silicon MEMS technology. Along with custom-designed 14-bit ADC ASIC, it offers the advantages of low noise, high accuracy, low power consumption, and offset trimming. The I<sup>2</sup>C serial bus allows for easy interface.

The QMA7981 is in a 2x2x0.95mm3 surface mount 12-pin land grid array (LGA) package.

# FEATURES

- 3-Axis Accelerometer in a 2x2x0.95 mm<sup>3</sup> Land Grid Array Package (LGA), guaranteed to operate over a temperature range of -40 °C to +85 °C.

- 14-Bit ADC with low noise accelerometer sensor

- I<sup>2</sup>C Interface with Standard and Fast modes.

- Built-In Self-Test

- Wide range operation voltage (1.71V To 3.6V) and low power consumption (2-50µA low power conversion current)

- RoHS compliant , halogen-free

- Built-in motion algorithm

# BENEFIT

- Small size for highly integrated products. Signals have been digitized and factory trimmed.

- High resolution allows for motion and tilt sensing

- High-Speed Interfaces for fast data communications.

- Enables low-cost functionality test after assembly in production

- Automatically maintains sensor's sensitivity under wide operation voltage range and compatible with battery powered applications

- Environmental protection and wide applications

- Low power and easy applications including step counting, sleep quality, gaming and personal navigation

Advanced Information

# CONTENTS

| CO | NTENTS                                                             | 2  |

|----|--------------------------------------------------------------------|----|

| 1  | INTERNAL SCHEMATIC DIAGRAM                                         | 3  |

|    | 1.1 Internal Schematic Diagram                                     | 3  |

| 2  | SPECIFICATIONS AND I/O CHARACTERISTICS                             | 4  |

|    | 2.1 Product Specifications                                         |    |

|    | 2.2 Absolute Maximum Ratings                                       | 5  |

|    | 2.3 I/O Characteristics                                            | 5  |

| 3  | PACKAGE PIN CONFIGURATIONS                                         | 5  |

|    | 3.1 Package 3-D View                                               | 5  |

|    | 3.2 Package Outlines                                               | 6  |

| 4  | EXTERNAL CONNECTION                                                | 9  |

|    | 4.1 Dual Supply Connection                                         | 9  |

|    | 4.2 Single Supply connection                                       |    |

| 5  | BASIC DEVICE OPERATION                                             |    |

|    | 5.1 Acceleration Sensors                                           | 10 |

|    | 5.2 Power Management                                               | 10 |

|    | 5.3 Power On/Off Time                                              | 11 |

|    | 5.4 Communication Bus Interface I <sup>2</sup> C and Its Addresses |    |

| 6  | MODES OF OPERATION                                                 | 12 |

|    | 6.1 Modes Transition                                               | 12 |

|    | 6.2 Description of Modes                                           | 14 |

| 7  | Functions and interrupts                                           | 14 |

|    | 7.1 STEP_INT                                                       | 14 |

|    | 7.2 DRDY_INT                                                       | 15 |

|    | 7.3 Interrupt configuration                                        |    |

| 8  | I <sup>2</sup> C COMMUNICATION PROTOCOL                            | 17 |

|    | 8.1 I <sup>2</sup> C Timings                                       | 17 |

|    | 8.2 I <sup>2</sup> C R/W Operation                                 | 17 |

| 9  | REGISTERS                                                          | 18 |

|    | 9.1 Register Map                                                   | 18 |

|    | 9.2 Register Definition                                            | 19 |

の の 睿

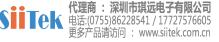

# 1 INTERNAL SCHEMATIC DIAGRAM

# 1.1 Internal Schematic Diagram

# Figure 1. Block Diagram

#### Table 1. Block Function

| Block                                                                                                  | Function                                       |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Transducer                                                                                             | 3-axis acceleration sensor                     |

| CVA                                                                                                    | Charge-to-Voltage amplifier for sensor signals |

| Interrupt Digital interrupt engine, to generate interrupt signal on data conver<br>and motion function |                                                |

| FSM Finite state machine, to control device in different mode                                          |                                                |

| I <sup>2</sup> C                                                                                       | Interface logic data I/O                       |

| OSC Internal oscillator for internal operation                                                         |                                                |

| Power                                                                                                  | Power block, including LDO                     |

# 2 SPECIFICATIONS AND I/O CHARACTERISTICS

# 2.1 **Product Specifications**

# Table 2. Specifications (\* Tested and specified at 25°C and 3.0V VDD except stated otherwise.)

| Parameter                           | Conditions                                                                                                    | Min  | Тур       | Max | Unit            |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------|------|-----------|-----|-----------------|

| Supply voltage VDD                  | VDD, for internal blocks                                                                                      | 1.71 | 3.3       | 3.6 | V               |

| I/O voltage VDDIO                   | VDDIO, for IO only                                                                                            | 1.71 | 3.3       | VDD | V               |

| Standby current                     | VDD and VDDIO on                                                                                              |      | 1         |     | μA              |

| Low power current                   | ODR=268 Hz                                                                                                    |      | 50        |     | μA              |

| Low power current                   | ODR=134 Hz                                                                                                    |      | 25.3      |     | μA              |

| Low power current                   | ODR=67 Hz                                                                                                     |      | 12.9      |     | μA              |

| Low power current                   | ODR=33.6 Hz                                                                                                   |      | 6.7       |     | μA              |

| Low power current                   | ODR=13.4 Hz                                                                                                   |      | 2.9       |     | μA              |

| Low power current                   | ODR=6.7 Hz                                                                                                    |      | 1.7       |     | μA              |

| Low noise current                   | ODR=32.5 Hz                                                                                                   |      | 100       |     | μA              |

| Low noise current                   | ODR=21.6 Hz                                                                                                   |      | 83.3      |     | μA              |

| Low noise current                   | ODR=13 Hz                                                                                                     |      | 50        |     | μA              |

| Low noise current                   | ODR=6.5 Hz                                                                                                    |      | 25        |     | μA              |

| BW                                  | Programmable bandwidth                                                                                        |      | 0.16~336  |     | Hz              |

| Data output rate<br>(ODR)           | 2*BW                                                                                                          |      | 0.32~672  |     | Samples<br>/sec |

| Startup time                        | From the time when VDD reaches<br>to 90% of final value to the time<br>when device is ready for<br>conversion |      | 2         |     | ms              |

| Wakeup time                         | e From the time device enters into active mode to the time device is ready for conversion                     |      | 1         |     | ms              |

| Operating<br>temperature            |                                                                                                               | -40  |           | 85  | °C              |

| Acceleration Full                   |                                                                                                               |      | ±2/±4/±8/ |     |                 |

| Range                               |                                                                                                               |      | ±16/±32   |     | g               |

| Sensitivity                         | FS=±2g                                                                                                        |      | 4096      |     | LSB/g           |

| Sensitivity                         | FS=±4g                                                                                                        |      | 2048      |     | LSB/g           |

| Sensitivity                         | FS=±8g                                                                                                        |      | 1024      |     | LSB/g           |

| Sensitivity                         | FS=±16g                                                                                                       |      | 512       |     | LSB/g           |

| Sensitivity                         | FS=±32g                                                                                                       |      | 256       |     | LSB/g           |

| Sensitivity                         |                                                                                                               |      |           |     |                 |

| Temperature Drift                   | FS=±2g, Normal VDD Supplies                                                                                   |      | ±0.02     |     | <b>%/℃</b>      |

| Sensitivity tolerance Gain accuracy |                                                                                                               |      | ±4        |     | %               |

| Zero-g offset                       | FS=±2g, Normal VDD Supplies                                                                                   |      | ±80       |     | mg              |

| Zero-g offset<br>Temperature Drift  | Zero-g offset                                                                                                 |      | ±2        |     | mg/℃            |

| Noise density                       | FS=±2g, run state                                                                                             |      | 200       |     | µg/sqrtHz       |

| Nonlinearity                        | $FS=\pm 2g$ , Best fit straight line,                                                                         |      | ±0.5      |     | %FS             |

| Cross Axis<br>Sensitivity           |                                                                                                               |      | 1         |     | %               |

# 2.2 Absolute Maximum Ratings

| Table 3. Absolute Maximum Ratings (Tested at 25°C except stated otherwis |

|--------------------------------------------------------------------------|

|--------------------------------------------------------------------------|

| Parameters          | Condition        | Min  | Max   | Units |

|---------------------|------------------|------|-------|-------|

| VDD                 |                  | -0.3 | 5.4   | V     |

| VDDIO               |                  | -0.3 | 5.4   | V     |

| ESD                 | НВМ              |      | 2     | kV    |

| Shock Immunity      | Duration < 200µS |      | 10000 | g     |

| Storage temperature |                  | -50  | 150   | °C    |

# 2.3 I/O Characteristics

## Table 4. I/O Characteristics

| Parameter      | Symbol            | Pin         | Condition      | Min.   | TYP. | Max.   | Unit |

|----------------|-------------------|-------------|----------------|--------|------|--------|------|

| Voltage Input  | V <sub>IH</sub> 1 | SDA, SCL    |                | 0.7*VD |      | VDDIO+ | V    |

| High Level 1   |                   |             |                | DIO    |      | 0.3    |      |

| Voltage Input  | V <sub>IL</sub> 1 | SDA, SCL    |                | -0.3   |      | 0.3*VD | V    |

| Low Level 1    |                   |             |                |        |      | DIO    |      |

| Voltage Output | V <sub>OH</sub>   | INT1, INT2  | Output Current | 0.8*VD |      |        | V    |

| High Level     |                   |             | ≥-100µA        | DIO    |      |        |      |

| Voltage Output | V <sub>OL</sub>   | INT1, INT2, | Output Current |        |      | 0.2*VD | V    |

| Low Level      | -                 | SDA         | ≤100µA(INT)    |        |      | DIO    |      |

|                |                   |             | Output Current |        |      |        |      |

|                |                   |             | ≤1mA (SDA)     |        |      |        |      |

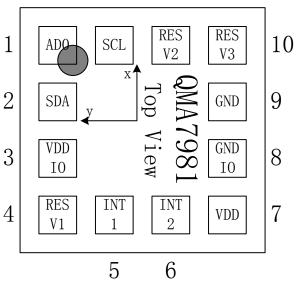

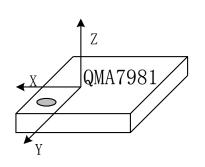

# **3 PACKAGE PIN CONFIGURATIONS**

# 3.1 Package 3-D View

Arrow indicates direction of g field that generates a positive output reading in normal measurement configuration.

## Figure 2. Package View

| PIN | PIN   | I/O | Power  | TYPE  | Function                          |  |

|-----|-------|-----|--------|-------|-----------------------------------|--|

| No. | NAME  |     | Supply |       |                                   |  |

| 1   | AD0   |     | VDDIO  | CMOS  | LSB of I <sup>2</sup> C address   |  |

| 2   | SDA   | 10  | VDDIO  | CMOS  | Serial data for I <sup>2</sup> C  |  |

| 3   | VDDIO |     | VDDIO  | Power | Power supply to digital interface |  |

| 4   | RESV1 |     | VDDIO  | CMOS  | Reserved. Float or connect to GND |  |

| 5   | INT1  | 0   | VDDIO  | CMOS  | Interrupt 1                       |  |

| 6   | INT2  | 0   | VDDIO  | CMOS  | Interrupt 2                       |  |

| 7   | VDD   |     | VDD    | Power | Power supply to internal block    |  |

| 8   | GNDIO |     | GND    | Power | Ground to digital interface       |  |

| 9   | GND   |     | GND    | Power | Ground to internal block          |  |

| 10  | RESV3 | 10  | VDDIO  | CMOS  | Reserved                          |  |

| 11  | RESV2 | 10  | VDDIO  | CMOS  | Reserved                          |  |

| 12  | SCL   | 1   | VDDIO  | CMOS  | Serial clock for I <sup>2</sup> C |  |

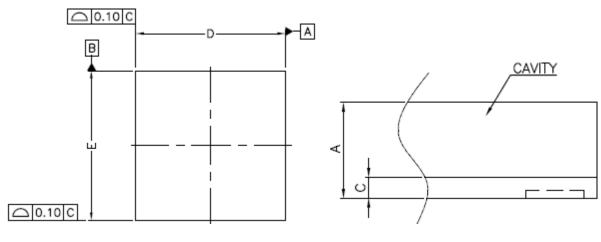

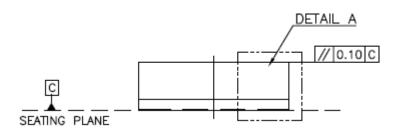

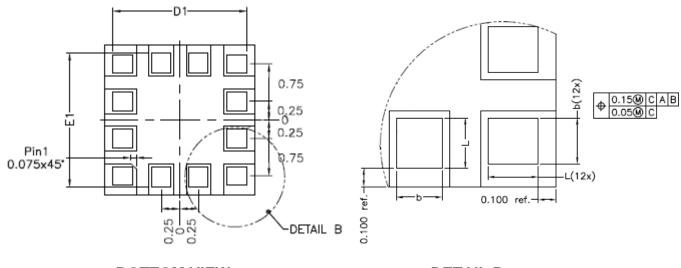

# 3.2 Package Outlines

3.2.1 Package Type

LGA (Land Grid Array)

## 3.2.2 Package Outline Drawing:

2.0mm (Length)\*2.0mm (Width)\*0.95mm (Height)

**TOP VIEW**

13-52-12

**BOTTOM VIEW**

DETAIL B

|        | D        | IMENSION | 1     | [     | IMENSIO | V     |

|--------|----------|----------|-------|-------|---------|-------|

| SYMBOL |          | (MM)     |       |       | (inch)  |       |

|        | MIN.     | NØM.     | MAX.  | MIN.  | NOM.    | MAX.  |

| Α      | 0.90     | 0.95     | 1.00  | 0.035 | 0.037   | 0.039 |

| С      | 0.16     | 0.20     | 0.24  | 0.006 | 0.008   | 0.009 |

| b      | 0.20     | 0.25     | 0.30  | 0.008 | 0.010   | 0.012 |

| D      | 1.95     | 2.00     | 2.05  | 0.077 | 0.079   | 0.081 |

| D1     |          | 1.80 BSC |       |       | .071 BS | С     |

| E      | 1.95     | 2.00     | 2.05  | 0.077 | 0.079   | 0.081 |

| E1     | 1.80 BSC |          |       | C     | .071 BS | С     |

| L      | Q.225    | 0.275    | 0.325 | 0.010 | 0.012   | 0.014 |

## NOTE:

1. CONTROLLING DIMENSION: MILLIMETER.

# Figure 3. Package Outline Drawing

## 3.2.3 Marking:

Figure 4. Marking Format

| Marking Text        | Description                               | Comments                                                                                                        |

|---------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Line 1 Product Name |                                           | "7981" stand for QMA7981                                                                                        |

| Line 2              | Y: the last digital of year CCC: lot code | Lot code: 3 alphanumeric digits, variable to generate mass production trace-code                                |

| Line 3              | P: Part number<br>S: Sub-con ID           | P: 1 alphanumeric digit, variable to identify part number<br>S: 1 alphanumeric digit, variable identify sub-con |

| •                   | Pin 1 identifier                          |                                                                                                                 |

# **4 EXTERNAL CONNECTION**

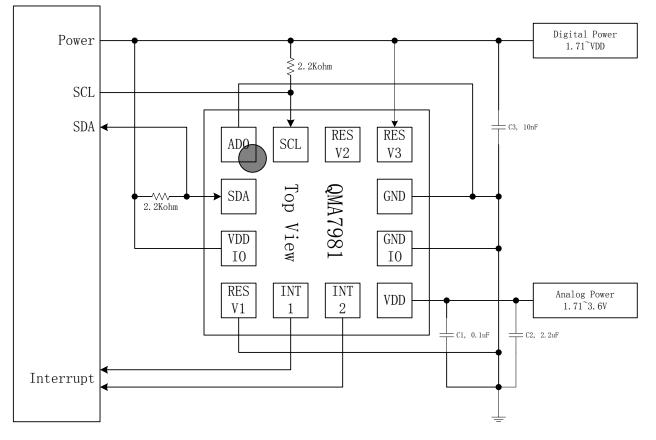

# 4.1 Dual Supply Connection

Figure 5. Dual Supply Connection

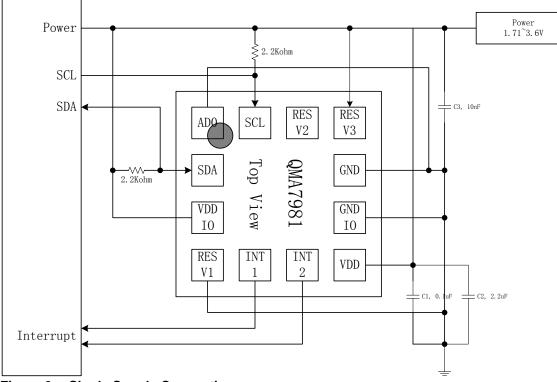

# 4.2 Single Supply connection

Figure 6. Single Supply Connection

# **5 BASIC DEVICE OPERATION**

# 5.1 Acceleration Sensors

The QMA7981 acceleration sensor circuit consists of tri-axial sensors and application specific support circuits to measure the acceleration of device. When a DC power supply is applied to the sensor, the sensor converts any accelerating incident in the sensitive axis directions to charge output.

# 5.2 **Power Management**

Device has two power supply pins. VDD is the main power supply for all of the internal blocks, including analog and digital. VDDIO is a separate power supply, for digital interface only.

The device contains a power-on-reset generator. It generates reset pulse as power on, which can load the register's default value, for the device to function properly.

To make sure the POR block functions well, we should have such constrains on the timing of VDD and VDDIO.

The device should turn-on both power pins in order to operate properly. When the device is powered on, all registers are reset by POR, then the device transits to the standby mode and waits for further commends.

Table 6 provides references for four power states.

## Table 6.Power States

| Power State | VDD        | VDDIO      | Power State description                                                                                                                                |

|-------------|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | 0V         | 0V         | Device Off, No Power Consumption                                                                                                                       |

| 2           | 0V         | 1.71v~3.6v | Not allowed. User need to make sure that VDDIO is<br>less than VDD. Otherwise, there will be leakage from<br>VDDIO to VDD through internal ESD devices |

| 3           | 1.71v~3.6v | 0          | Device Off, Same Current as Standby Mode                                                                                                               |

| 4           | 1.71v~3.6v | 1.71v~VDD  | Device On, Normal Operation Mode, Enters Standby Mode after POR                                                                                        |

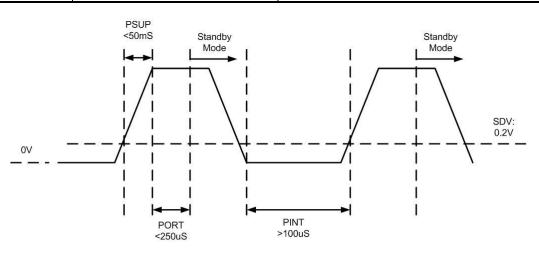

# 5.3 Power On/Off Time

After the device is powered on, some time periods are required for the device fully functional. The external power supply requires a time period for voltage to ramp up (PSUP), typically 50 milli-second. However it isn't controlled by the device. The Power–On–Reset time period (PORT) includes time to reset all the logics, load values in NVM to proper registers, enter the standby mode and get ready for analogy measurements. The power on/off time related to the device is in Table 7

## Table 7. Time Required for Power On/Off

| Parameter     | Symbol | Condition                              | Min. | Тур. | Max. | Unit |

|---------------|--------|----------------------------------------|------|------|------|------|

| POR           | PORT   | Time Period After VDD and              |      |      | 250  | μs   |

| Completion    |        | VDDIO at Operating Voltage to          |      |      |      |      |

| Time          |        | Ready for I <sup>2</sup> C Commend and |      |      |      |      |

|               |        | Analogy Measurement.                   |      |      |      |      |

| Power off     | SDV    | Voltage that Device Considers          |      |      | 0.2  | V    |

| Voltage       |        | to be Power Down.                      |      |      |      |      |

| Power on      | PINT   | Time Period Required for               | 100  |      |      | μs   |

| Interval      |        | Voltage Lower Than SDV to              |      |      |      |      |

|               |        | Enable Next POR                        |      |      |      |      |

| Power on Time | PSUP   | Time Period Required for               |      |      | 50   | ms   |

|               |        | Voltage from SDV to 90% of             |      |      |      |      |

|               |        | final value                            |      |      |      |      |

## Power On/Off Timing

# Figure 7. Power On/Off Timing

# 5.4 Communication Bus Interface I<sup>2</sup>C and Its Addresses

This device will be connected to a serial interface bus as a slave device under the control of a master device, such as the processor. Control of this device is carried out via I<sup>2</sup>C.

This device is compliant with I<sup>2</sup>C -Bus Specification, document number: 9398 393 40011. As an I<sup>2</sup>C compatible device, this device has a 7-bit serial address and supports I<sup>2</sup>C protocols. This device supports standard and fast speed modes, 100 kHz and 400 kHz, respectively. External pull-up resistors are required to support all these modes.

There are two  $I^2C$  addresses selected by connecting pin 1 (AD0) to GND or VDDIO. The first six MSB are hardware configured to "001001" and the LSB can be configured by AD0.

# Table 8. I<sup>2</sup>C Address Options

| AD0 (pin 1)      | I <sup>2</sup> C Slave Address(HEX) | I <sup>2</sup> C Slave Address(BIN) |

|------------------|-------------------------------------|-------------------------------------|

| Connect to GND   | 12                                  | 0010010                             |

| Connect to VDDIO | 13                                  | 0010011                             |

# **6 MODES OF OPERATION**

# 6.1 Modes Transition

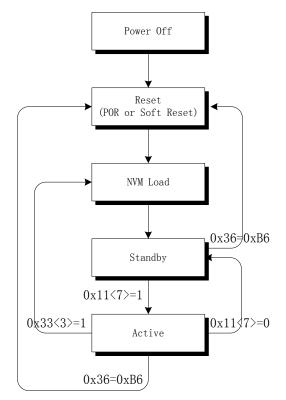

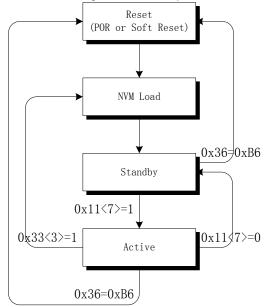

QMA7981 has two different operational modes, controlled by register (0x11), MODE\_BIT. The main purpose of these modes is for power management. The modes can be transited from one to another, as shown below, through I<sup>2</sup>C commands. The default mode after power-on is standby mode.

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or |

|-----------------------------------------------------------------------------------------------------------------|

| disclosed in whole or in part without prior written permission of QST.                                          |

## Figure 8. Basic operation flow after power-on

The default mode after power on is standby mode. Through  $I^2C$  instruction, device can switch between standby mode and active mode. With SOFTRESET by writing 0xB6 into register 0x36, all of the registers will get default values. SOFTRESET can be done both in active mode and in standby mode. Also, by writing 1 in NVM\_LOAD (0x33<3>) when device is in active mode, the NVM related image registers will get default value from NVM, however, other registers will keep the values of their own.

Figure 9. The work mode transferring

# 6.2 Description of Modes

# 6.2.1 Active Mode

In active mode, the ADC digitizes the charge signals from transducer, and digital signal processor conditions these signals in digital domain, processes the interrupts, and send data to Data registers (0x01~0x06).

## 6.2.2 Standby Mode

In standby mode, most of the blocks are off, while device is ready for access through  $I^2C$ . Standby mode is the default mode after power on or soft reset. Device can enter into this mode by set the soft reset register (0x36) to 0xB6 or set the MODE\_BIT (0x11<7>) to logic 0.

Besides the above two modes, the device also contains NVM loading state. This state is used to reset the value of the NVM related image registers. There are two bits related to this state. When NVM\_LOAD (0x33<3>) is set to 1, NVM loading starts. When the device is in NVM loading state, NVM\_RDY (0x33<2>) is set to logic 0 by device. After NVM loading is finished, NVM\_RDY (0x33<2>) is set back to logic 1 by device, and NVM\_LOAD is reset to 0 by device automatically. NVM loading can only happen when NVM\_LOAD is set to 1 in active mode. If the user sets this NVM\_LOAD bit to 1 in standby mode, the device will not take the action until it enters into active state by setting MODE\_BIT (0x11<7>) to logic 1.

After loading NVM, the device will enter into standby mode directly.

The loading time for NVM is about 100uS.

# 7 Functions and interrupts

ASIC support interrupts, such as STEP\_INT, DRDY\_INT

# 7.1 STEP\_INT

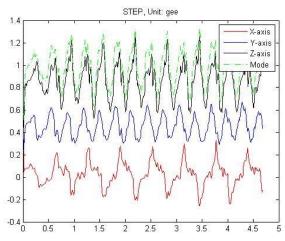

The STEP/STEP\_QUIT detect that the user is entering/exiting step mode. When the user enter into step mode, at least one axis sensor data will vary periodically, by numbering the variation periods the step counter can be calculated.

Median data (max+min) /2 is called dynamic threshold, the max and min data can be updated by certainly samples, the sample number can be set by register STEP\_SAMPLE\_CNT (0x12<4:0>). When the sensor data decreasing (or increasing) through the dynamic threshold, a user run step is detected.

Register STEP\_PRECISION (0x13<6:0>) is used as threshold when updating the new collected sensor data. Sensor data below the threshold will be discarded, this helps removing unstable variations causing failed detection.

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or | 14 / 25 |

|-----------------------------------------------------------------------------------------------------------------|---------|

| disclosed in whole or in part without prior written permission of QST.                                          | 14 / 23 |

The run step event happened at certain interval timing. All of the events outside the timing window will not be regarded as a run step and the step counter will not counted. The timing window can be set by register STEP\_TIME\_UP(0x15) and STEP\_TIME\_LOW(0x14), the conversion ODR numbers ranged from STEP\_TIME\_LOW \*ODR to 8\* STEP\_TIME\_UP\*ODR. Also if no new run step event detected until the up limited timing threshold, STEP\_QUIT INT will generation.

To remove unstable variation which will cause false STEP event detection, the step counter considers steps as valid step events only after 4 continuous steps detected. Also, the step counter register STEP\_CNT\_/ STEP\_CNT\_MSB (0x07,0x08) will be updated immediately by value 4, and interrupt STEP is also generated.

The related interrupt status bit is STEP\_INT (0x0A<3>) and STEP\_QUIT\_INT (0x0A<2>). When the interrupt is generated, the value of STEP\_INT/ STEP\_QUIT\_INT will be set to logic 1, which will be cleared after the interrupt status register is read by user. STEP\_EN/STEP\_QUIT\_EN (0x16<3>/0x16<2>) is the enable bit for the STEP\_INT/STEP\_QUIT\_INT. Also, to get this interrupt on PIN\_INT1 and/or PIN\_INT2, we need to set INT1\_STEP (0x19<3>)/INT1\_STEP\_QUIT (0x19<2>) or INT2\_STEP (0x1B<3>) /INT2\_STEP\_QUIT (0x1B<2>) to logic 1, to map the interrupt to the interrupt PINs.

# 7.2 DRDY\_INT

The width of the acceleration data is 14 bits, in two's complement representation. The data of each axis is split into 2 parts, the MSB part (one byte contains bit 13 to bit 6) and the LSB part (one byte contains bit 5 to bit 0). Reading data should start with LSB part. When user is reading the LSB byte of data, to ensure the integrity of the acceleration data, the content of MSB can be locked, by setting SHADOW\_DIS (0x21<6>) to logic 0. This lock function can be disabled by setting SHADOW\_DIS to logic 1. Without lock, the MSB and LSB content will be updated by new value immediately. The bit NEW\_DATA in the LSB byte is the flag of the new data. If new data is updated, this NEW\_DATA flag will be 1, and will be cleared when corresponding MSB or LSB is read by user. Also, the user should note that even with SHADOW\_DIS=0, the data of 3 axes are not guaranteed from the same time point.

| RANGE  | Acceleration<br>range | Resolution |

|--------|-----------------------|------------|

| 0001   | 2g                    | 244ug/LSB  |

| 0010   | 4g                    | 488ug/LSB  |

| 0100   | 8g                    | 977ug/LSB  |

| 1000   | 16g                   | 1.95mg/LSB |

| 1111   | 32g                   | 3.91mg/LSB |

| Others | 2g                    | 244ug/LSB  |

The device supports four different acceleration measurement ranges. The range is setting through RANGE (0x0F<3:0>), and the details as following:

The interrupt for the new data serves for the synchronous data reading for the host. It is generated after storing a new value of z-axis acceleration data into data register. This interrupt will be cleared automatically when the next data conversion cycle starts, and the interrupt will be effective about 64\*MCLK, and automatically cleared. The interrupt mode for the new data is fixed to be non-latched.

# 7.3 Interrupt configuration

The device has the above 3 interrupt engines. Each of the interrupts can be enabled and configured independently. If the trigger condition of the enabled interrupt fulfilled, the corresponding interrupt status bit will be set to logic 1, and the mapped interrupt pin will be activated. The device has two interrupt PINs, INT1 and INT2. Each of the interrupts can be mapped to either PIN or both PINs.

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or | 15 / 25 |

|-----------------------------------------------------------------------------------------------------------------|---------|

| disclosed in whole or in part without prior written permission of QST.                                          | 15725   |

The interrupt status registers update when a new data word is written into the data registers. If an interrupt is disabled, the related active interrupt status bit is disabled immediately.

Device supports 2 interrupt modes, non-latched, and latched mode. The interrupt modes are set through LATCH\_INT (0x21<0>).

In non-latched mode, the interrupt status bit and the mapped interrupt pin are cleared as soon as the associated conditions are no more valid, or read operation to the INT\_STAT (0x09~0x0d). Exceptions to this are the new data, orientation, and flat interrupts, which are automatically reset after a fixed time.

In latched mode, the clearings of the interrupt status and selected pin are determined by INT\_RD\_CLR (0x21<7>). If INT\_RD\_CLR=0, read operation to the INT\_STAT will clear the interrupt and the selected pin. If INT\_RD\_CLR=1, any read operation to the device will clear the interrupt and the selected pin.

If the condition for trigging the interrupt still holds, the interrupt status will be set again with the next change of the data registers.

Mapping the interrupt pins can be set by INT\_MAP (0x19~0x1B).

The electrical interrupt pins can be set in INT\_PIN\_CONF (0x20<3:0>). The active logic level can be set to 1 or 0, and the interrupt pin can be set to open-drain or push-pull.

If the interrupt mode is configured as latched mode, the interrupt can also be cleared by  $I^2C$  reading any of the interrupt status register (0x09 ~ 0x0d).

# 8 I<sup>2</sup>C COMMUNICATION PROTOCOL

# 8.1 I<sup>2</sup>C Timings

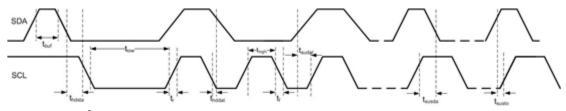

Table 9 and Figure 11 describe the I<sup>2</sup>C communication protocol times

13-52-12

# Table 9. I<sup>2</sup>C Timings

| Parameter        | Symbol             | Condition | Min. | Тур. | Max. | Unit |

|------------------|--------------------|-----------|------|------|------|------|

| SCL Clock        | f <sub>scl</sub>   |           | 0    |      | 400  | kHz  |

| SCL Low Period   | t <sub>low</sub>   |           | 1    |      |      | μs   |

| SCL High Period  | t <sub>high</sub>  |           | 1    |      |      | μs   |

| SDA Setup Time   | t <sub>sudat</sub> |           | 0.1  |      |      | μs   |

| SDA Hold Time    | t <sub>hddat</sub> |           | 0    |      | 0.9  | μs   |

| Start Hold Time  | t <sub>hdsta</sub> |           | 0.6  |      |      | μs   |

| Start Setup Time | t <sub>susta</sub> |           | 0.6  |      |      | μs   |

| Stop Setup Time  | t <sub>susto</sub> |           | 0.6  |      |      | μs   |

| New Transmission | t <sub>buf</sub>   |           | 1.3  |      |      |      |

| Time             |                    |           |      |      |      | μs   |

| Rise Time        | t <sub>r</sub>     |           |      |      |      | μs   |

| Fall Time        | t <sub>f</sub>     |           |      |      |      | μs   |

Figure 11. I<sup>2</sup>C Timing Diagram

# 8.2 I<sup>2</sup>C R/W Operation

## 8.2.1 Abbreviation

## Table 10. Abbreviation

| SACK | Acknowledged by slave      |

|------|----------------------------|

| MACK | Acknowledged by master     |

| NACK | Not acknowledged by master |

| RW   | Read/Write                 |

## 8.2.2 Start/Stop/Ack

START: Data transmission begins with a high to transition on SDA while SCL is held high. Once I<sup>2</sup>C transmission starts, the bus is considered busy.

STOP: STOP condition is a low to high transition on SDA line while SCL is held high.

ACK: Each byte of data transferred must be acknowledged. The transmitter must release the SDA line during the acknowledge pulse while the receiver mush then pull the SDA line low so that it remains stable low during the high period of the acknowledge clock cycle.

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or |  |

|-----------------------------------------------------------------------------------------------------------------|--|

| disclosed in whole or in part without prior written permission of QST.                                          |  |

| <b>q</b> ぱ <sub>砂睿</sub> |

|--------------------------|

|--------------------------|

NACK: If the receiver doesn't pull down the SDA line during the high period of the acknowledge clock cycle, it's recognized as NACK by the transmitter.

## 8.2.3 I<sup>2</sup>C Write

I<sup>2</sup>C write sequence begins with start condition generated by master followed by 7 bits slave address and a write bit (R/W=0). The slave sends an acknowledge bit (ACK=0) and releases the bus. The master sends the one byte register address. The slave again acknowledges the transmission and waits for 8 bits data which shall be written to the specified register address. After the slave acknowledges the data byte, the master generates a stop signal and terminates the writing protocol.

## Table 11. I<sup>2</sup>C Write

| ST  | Slave Address | R<br>W | S/  | R   | egis | ter<br>(0x <sup>-</sup> |   | dres | SS |   | Ś   |   |   | ( | Da<br>(0x) |   |   |   |   | Ś   | Ŋ   |

|-----|---------------|--------|-----|-----|------|-------------------------|---|------|----|---|-----|---|---|---|------------|---|---|---|---|-----|-----|

| ART | 0 0 1 0 0 1 0 | 0      | АСК | 0 0 | 0    | 1                       | Ó | 0    | 0  | 1 | ACK | 1 | 0 | 0 | 0          | 0 | 0 | 0 | 0 | ACK | ΓΟΡ |

# 8.2.4 I<sup>2</sup>C Read

$I^2C$  write sequence consists of a one-byte  $I^2C$  write phase followed by the  $I^2C$  read phase. A start condition must be generated between two phase. The  $I^2C$  write phase addresses the slave and sends the register address to be read. After slave acknowledges the transmission, the master generates again a start condition and sends the slave address together with a read bit (R/W=1). Then master releases the bus and waits for the data bytes to be read out from slave. After each data byte the master has to generate an acknowledge bit (ACK = 0) to enable further data transfer. A NACK from the master stops the data being transferred from the slave. The slave releases the bus so that the master can generate a STOP condition and terminate the transmission.

The register address is automatically incremented and more than one byte can be sequentially read out. Once a new data read transmission starts, the start address will be set to the register address specified in the current I<sup>2</sup>C write command.

# Table 12. I<sup>2</sup>C Read

| ST    |   | Sl  | ave | Ac   | ldre        | ess |   | R<br>W | S    | Register Address<br>(0x00) |                |   |   |   |   |   |      |      |                |   |   |           |            |   |   |      |      |   |

|-------|---|-----|-----|------|-------------|-----|---|--------|------|----------------------------|----------------|---|---|---|---|---|------|------|----------------|---|---|-----------|------------|---|---|------|------|---|

| START | 0 | 0   | 1   | 0    | 0           | 1   | 0 | 0      | SACK | 0                          | 0              | 0 | 0 | 0 | 0 | 0 | 0    | SACK |                |   |   |           |            |   |   |      |      |   |

| ST    |   | Sla | ave | e Ac | ldre        | ess |   | R<br>W | SA   |                            | Data<br>(0x00) |   |   |   |   |   |      |      | Data<br>(0x01) |   |   |           |            |   |   |      |      |   |

| START | 0 | 0   | 1   | 0    | 0           | 1   | 0 | 1      | ACK  | 0                          | 0              | 0 | 0 | Ó | 0 | 1 | 0    | MACK | 0              | 0 | 0 | 0         | 0          | 0 | 0 | 0    |      |   |

| M,    |   |     |     |      | )ata<br>x02 |     |   |        | MA   |                            |                |   |   |   |   |   |      | Ň    |                |   |   | Da<br>(0x | ata<br>07) |   |   |      | ź    | S |

| MACK  | 0 | 0   | 0   | Ò    | 0           | 0   | 1 | 0      | ACK  | ····                       |                |   |   |   |   |   | MACK | 0    | 0              | 0 | 0 | 0         | 0          | 0 | 0 | NACK | STOP |   |

# 9 REGISTERS

# 9.1 Register Map

The table below provides a list of the 8-bit registers embedded in the device and their respective function and addresses

## Table 13. Register Map

| Add.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Name                                                        | bit7                                                                                                                                            | bit6                         | bit5        | bit4                                                              | bit3                                                                                                                                 | bit2            | bit1          | bit0                   | R/W                                                                                  | DEF                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 0x3F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             |                                                                                                                                                 |                              |             |                                                                   | -                                                                                                                                    | 1               |               |                        | R                                                                                    | 00                                                                         |

| 0x3E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             | OLTN: 7/7 O                                                                                                                                     |                              |             |                                                                   |                                                                                                                                      |                 |               |                        | RW<br>RW                                                                             | 00<br>NVM                                                                  |

| 0x3D<br>0x3C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             | GAIN_Z<7:0><br>GAIN_Y<7:0>                                                                                                                      |                              |             |                                                                   |                                                                                                                                      |                 |               |                        | RW<br>RW                                                                             | NVM                                                                        |

| 0x3E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             | GAIN X<7:0>                                                                                                                                     |                              |             |                                                                   |                                                                                                                                      |                 |               |                        | RW                                                                                   | NVM                                                                        |

| 0x3A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                           | OFFSET_Z<7:0>                                                                                                                                   |                              |             |                                                                   |                                                                                                                                      |                 |               |                        | RW                                                                                   | NVM                                                                        |

| 0x39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             | OFFSET_Y<7:0>                                                                                                                                   |                              |             |                                                                   |                                                                                                                                      |                 |               |                        | R₩                                                                                   | NVM                                                                        |

| 0x38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             | OFFSET_X<7:0>                                                                                                                                   |                              |             |                                                                   |                                                                                                                                      | 1               |               |                        | RW                                                                                   | NVM                                                                        |

| 0x37<br>0x36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IMAGE<br>S RESET                                            | OFFSET_X<10:8                                                                                                                                   | s><br>B6 / NVM UNLOC         | W. 0        | GAIN_                                                             | Z<9:8>                                                                                                                               | I               | OFFSET_Y<10:8 | >                      | RW<br>RW                                                                             | NVM<br>00                                                                  |

| 0x36<br>0x35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             | SUFIRESET: UX                                                                                                                                   | DO / NVM_UNLUC               | N: UXD3     | 1                                                                 |                                                                                                                                      | 1               | 1             |                        | R                                                                                    | FF                                                                         |